## Neutron Monitor Workshop 2(B): Neutron Monitor Digital Electronics

Mahidol University

June 26, 2009

Paul Evenson University of Delaware

Cosray at McMurdo Station

# Workshop Series Plan

- 1. Detector operation

- A. Detector Physics and Analog Electronics

- B. Art and Science of Soldering

- 2. Digital Circuits

- A. Principles of Digital Logic

- B. Neutron Monitor Digital Electronics

- 3. Microcontrollers

- 4. Real time data acquisition

- A. Principles of Telemetry and Data Acquisition

- B. Data Conversion and Manipulation with Visual Basic

### **Plan For Today**

- Discussion of Design Problem Solutions

- FIFO's and Microcontrollers

- Questions and answers

- System Overview

- Questions and answers

- Schematics in Detail

- Tour of several PDF files

- Questions and answers

## FIFO's and Microcontrollers

- I start with a discussion of two LSI (Large Scale Integrated) circuits that are ubiquitous in the neutron monitor system:

- First-In First Out (FIFO) memory

- Microcontrollers

### First In First Out (FIFO) Memory

- The FIFO allows a data source and a data user to operate asynchronously

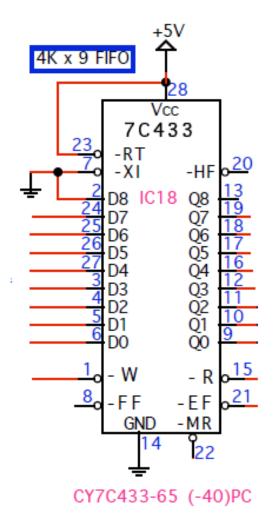

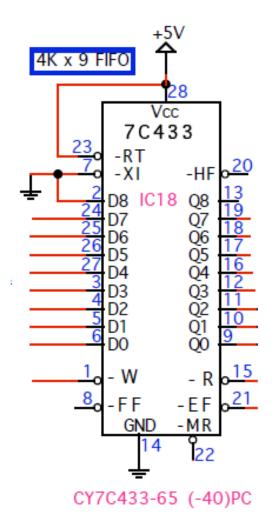

- This device stores up to 4096 9-bit "words" with minimal control overhead

- There is no addressing the words are read out in the order in which they are put in – "First In – First Out"

### **FIFO Inputs and Outputs**

- Inputs

- Data lines D0 ... D8

- Write strobe (-W)

- Read strobe (-R)

- Master Reset (-MR)

- Grouping (-RT, -XI)

- Outputs

- Data lines Q0 ... Q8

- Empty (-EF)

- Half Full (-HF)

- Full (-FF)

### **Control Logic**

- Note the increasing complexity of the logic in the following problems, particularly in the need for proper sequencing of multiple clocks

- Initializing and completing a sequence can be particularly tedious

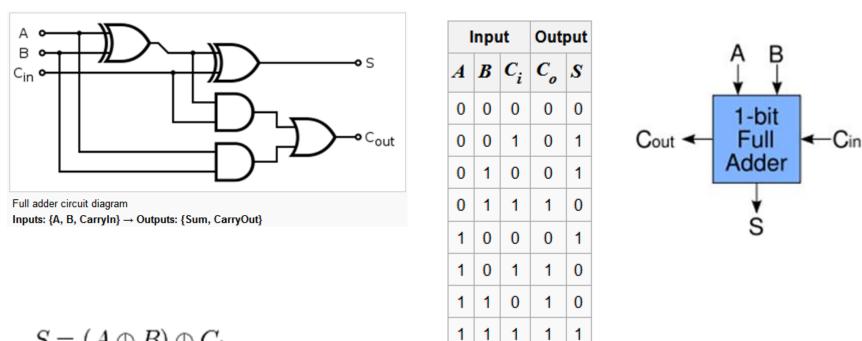

### **Problem 4: Answer Is Just Gates**

1

1

$S = (A \oplus B) \oplus C_{in}$

$$C_{out} = (A \cdot B) + (C_{in} \cdot (A \oplus B)) = (A \cdot B) + (C_{in} \cdot B) + (C_{in} \cdot A)$$

### Problem 5: Design an 8 Bit "Accumulator" to Add 4 Bit Numbers

- An accumulator is an array of memory cells to which successive numbers can be added

- Use four of the switches for input

- Use one of the push buttons as a clock

- Display the results in the lights

- My approach would be to latch the outputs of a a chain of full adders into D flipflops

- The Q output of each D would feed back into that stage of the adder

- Initialization and operation are handled by the human

### Problem 6: Design a Circuit to Multiply Two 4 Bit Numbers

- Multiplying two, four bit numbers yields an eight bit product

- This actually could be implemented with a lot of gates, since there is an 8 bit

→ 8 bit truth table that uniquely specifies the answer, but here you should do it with clocked logic

- Use two groups of four switches for the inputs

- Display the product in the lights

- Use a push button to initiate the clock sequence

- My approach would be to use two shift registers and an accumulator

- Some of the control is still in the human

- Getting the proper clock sequence, and making it stop at the right point requires some significant effort in logic

### FPGA's and Microcontrollers

- There are two main solutions to this issue, both of which are chips with multiple, independent input and output pins

- The function and timing of each pin is controlled by a program internal to the chip

### FPGA's and Microcontrollers

- Field Programmable Gate Array

- Huge numbers (millions) of individual gates on one chip that can be electronically interconnected by loading a program

- Highly advanced software to translate logic equations (refer to the full adder problem) into the program

- Many "gate logic" functions can be completed simultaneously

- Microcontroller

- "One chip computer" with internal memory

- Programmed like a computer so it can do arithmetic and make fairly complex decisions

- Because of this linear sequence the operation is "slow"

- Using these is the subject of the next workshop

- Chips combining both are also available

### **System Overview**

| Slot# | 21 | 20    | 17              | 14              | 11              | 10             | 9 | 8 | 7        | 6 | 5 | 4        | 3 | 2 | 1  |   |

|-------|----|-------|-----------------|-----------------|-----------------|----------------|---|---|----------|---|---|----------|---|---|----|---|

| 0     |    | Spare | Digiquartz<br>3 | Digiquartz<br>2 | Digiquartz<br>1 | Serial Fan-Out |   |   | Master 0 |   |   | Master 3 |   |   | ar | 0 |

#### Cosray 2000 Rack, Front View

Notes:

- 1) The 19" rack is a Vector CCA 14S/90 for 4.5" X 9.5" boards with 21 slots at 0.75" centers, and only 15 slots with connectors.

- 2) The spare slots are wired like the GPS and Master slots, and have individual Readout select lines.

- 3) Slots 10, 9 and 8 are designated for the Counter Expansion (or Serial Fan-out), Counter, and Readout boards respectively and exclusively.

- 4) A Counter Expansion Input board would allow access to the 10 counter channels in case the barometers are not mounted in the rack, or other signals need counting. This is slot 10 and is currently used for serial expansion.

- 5) Master boards may be placed in any slot. Master 3 located in Slot 4 is only used at South Pole.

- 6) Up to 3 Digiquartz barometers may occupy 3 slots in locations 11, 14, and 17.

- 8) The slots behind the Digiquartz barometers (12,13,15,16,18,19) do no require connectors or guide rails.